Hello Pupils! I welcome you to The Engineering Projects. I hope you are having a good day. In our previous lecture, we discussed Half-Adder Circuit Designing with XOR and AND logic gates. Today, we are going to design the same circuit using universal logic gates i.e. NOR and NAND gates.

We are going to learn the following topics, in today's lecture:

- What is Adder?

- What is Half Adder?

- How can We make Half Adder Circuit through NAND Gate?

- How can We make Half Adder through just NOR Gate?

Hence without wasting time, Let's find all the Answers.

What is Adder?

As we discussed in the last lecture, the DLD Adder is a simple electronic circuit, used to add binary numbers in bit form.

There are two types of DLD Adders, named:

- Half Adder

- Full Adder

In this article, we'll focus on the Half Adder only.

What is Half Adder?

Let's recall it as well from our previous lecture, a Half Adder is a simple electronic circuit, designed with logic gates and is used to add two binary numbers. It generates two output bits i.e. Sum Bit and Carry Bit.

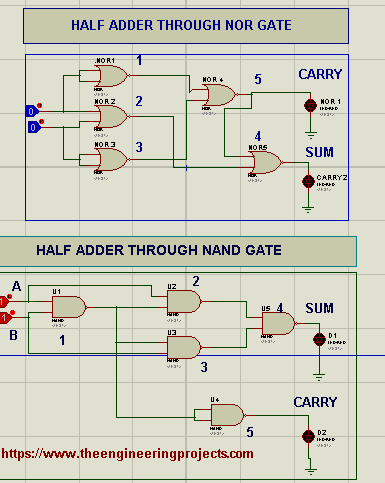

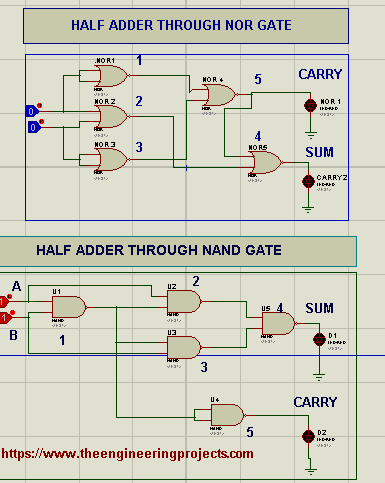

In our previous lecture, we designed the Half Adder using two types of Logic Gates i.e. AND and XOR but today, we are going to use a single type of logic gate(Universal Gate) to design a Half Adder. As we know there are two universal gates in DLD i.e. NOR and NAND. So, we will design the Half Adder circuit with both of these Universal Gates, shown in the below figure:

Truth Table of Half Adder

- The Truth Table of the Half Adder is shown in the below table:

| Input | Output | ||

| A | B | Sum |

C0 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Half Adder with NAND Gate

Let's first recall the NAND Gate:

"A NAND Gate is an inversion of AND Gate and gives LOW output if all of its Inputs are HIGH, otherwise gives HIGH output".

The Truth Table of NAND Gate is shown below:

| A | B | (A.B)' |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Let's rush towards the Proteus software to run our Half Adder.

Components Required

We will need the following components to design Half Adde circuit in Proteus:

- NAND Gate

- Logic Toggle

- LED

- Ground Terminal

Proteus Simulation of Half Adder

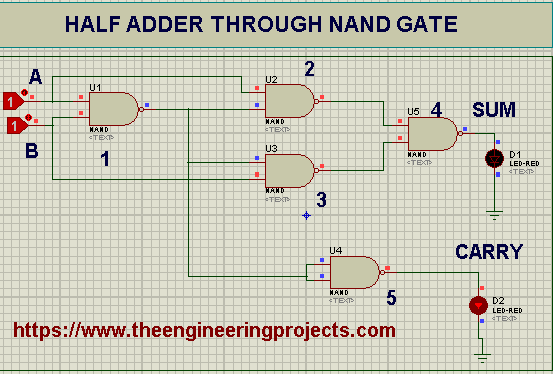

- Here's the Circuit Diagram of the Half Adder with the NAND gate in Proteus:

- For designing the Half Adder circuit, we'll need 5 NAND gates in total, so get them from Proteus Library and place them in the Workspace, as shown in the above figure.

- I have used two Logic States at the Inputs and two LEDs at the Outputs.

In order to understand this Half Adder circuit, let's create a truth table of output at each NAND Gate:

| Input | Output | |||||

| A | B | 1 | 2 | 3 | 4(SUM) | 5(CARRY) |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 |

Half Adder with NOR Gate

Let's recall the NOR Gate from our previous lecture:

"A NOR Gate is an inversion of the OR Gate and gives HIGH Output only if all of its Inputs are LOW, otherwise it gives LOW".

The Truth Table of NOR Gate is as follows:

| A | B | (A+B)’ |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

To implement the Half Adder with NOR Gate, we are going to use the below components:

Components Required:

- NOR Gate.

- Logic Toggle.

- LED.

- Ground Terminal.

- Connecting wires.

Proteus Simulation of Half Adder

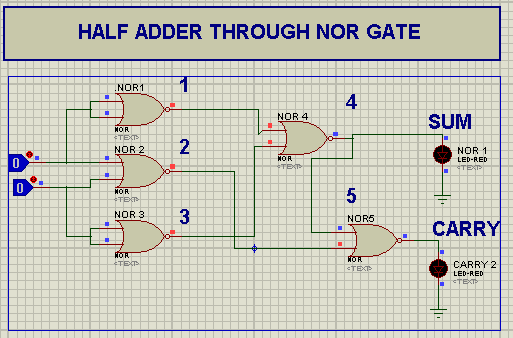

Here's the circuit diagram of the Half Adder with NOR logic gate:

As you can see in the above figure, we have used 5 NOR gates in total and have placed logic states at the inputs and LEDs at the outputs.

Here's the truth table of Half Adder with NOR Gate:

| Input | Output | |||||

| A | B | 1 | 2 | 3 | 4(SUM) | 5(CARRY) |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 |

So, that was all for today. In the next lecture, we will discuss the 2-Bit Full Adder in detail and will simulate it in Proteus. Thanks for reading.